编者荐语:

MIPI (Mobile Industry Processor Interface)协议是 MIPI 联盟(MIPI Alliance)提出的用于标准化移动终端系统各器件间通信的通信协议。听听协会理事单位智微电子对MIPI RFFE协议的技术解读吧!

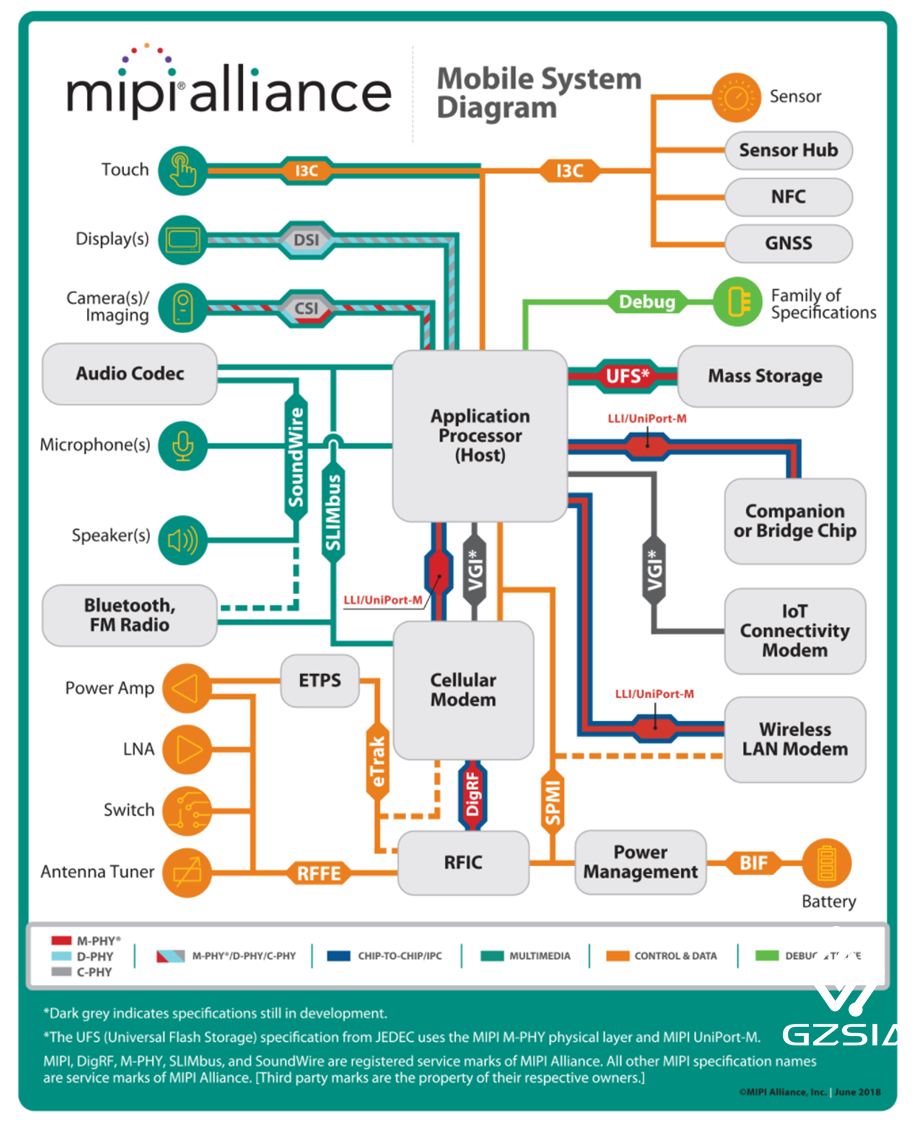

MIPI (Mobile Industry Processor Interface)协议是 MIPI 联盟(MIPI Alliance)提出的用于标准化移动终端系统各器件间通信的通信协议。MIPI联盟2003年成立,最早的初衷是为了标准化显示接口。

图:MIPI联盟最早于2003年成立

经过多年发展,截止2019年12月,MIPI联盟已经发布48份标准,应用领域也扩展至汽车、工业及AR/VR等领域。MIPI联盟拥有包括终端厂商、器件厂商、平台厂商以及测试厂商在内的339个会员单位。MIPI协议成为手机终端各器件通信的主流标准协议。

图:MIPI联盟所涉及的技术领域及应用领域

MIPI RFFE(MIPI RF Front-end,MIPI射频前端)是MIPI联盟RFFE工作组在2010年推出的用于移动终端射频前端控制的控制接口标准。

在MIPI RFFE推出之前,射频前端的控制解决方案复杂,如果用并行的GPIO口进行控制,需要接口过多,系统成本无法承载;一些厂商开始自定义串口控制,不过由于通信协议复杂,需要考虑复杂的软件控制和时序控制,实现困难,并且自定义串口也不利于不同厂商器件的通信。

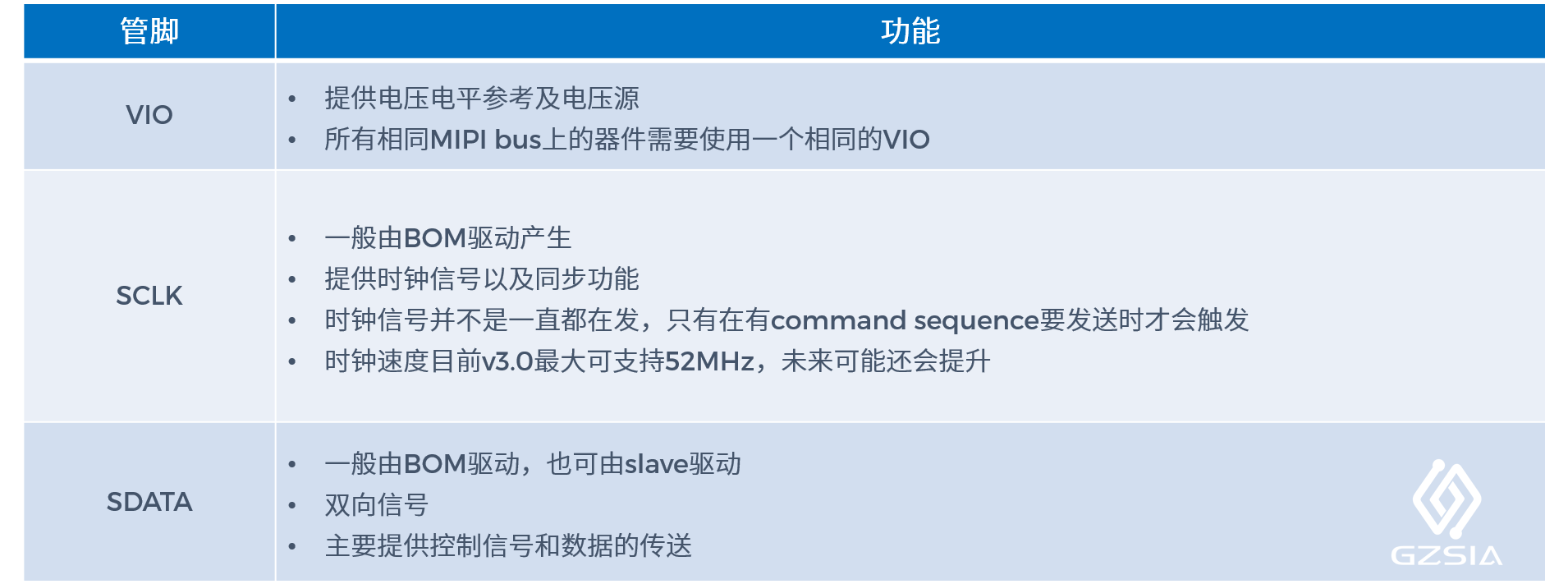

2010年,MIPI联盟推出用于射频前端控制的MIPI RFFE协议。MIPI RFFE协议总线由一根电源线(VIO)以及两根控制线(SCLK和SDATA)构成,实现简单,易于部署,可实现时序范围要求内的近实时控制。

图:MIPI RFFE V1.0中所提出的系统架构

在过去10年中,无线终端通信协议从3G演进至4G、5G,MIPI协议也不断演进。目前,MIPI协议已演进至V3.0版本,支持多种Trigger模式,适应5G通信系统中更多器件以及更严苛的时序控制要求。各个MIPI版本演进时增加的主要特性如下:

慧智微电子在MIPI RFFE协议的V1.x时代加入MIPI联盟RFFE工作组,对MIPI RFFE协议技术演进长期关注。以下将对MIPI RFFE协议的技术进行讨论。

01 MIPI RFFE协议解读

MIPI RFFE系统架构

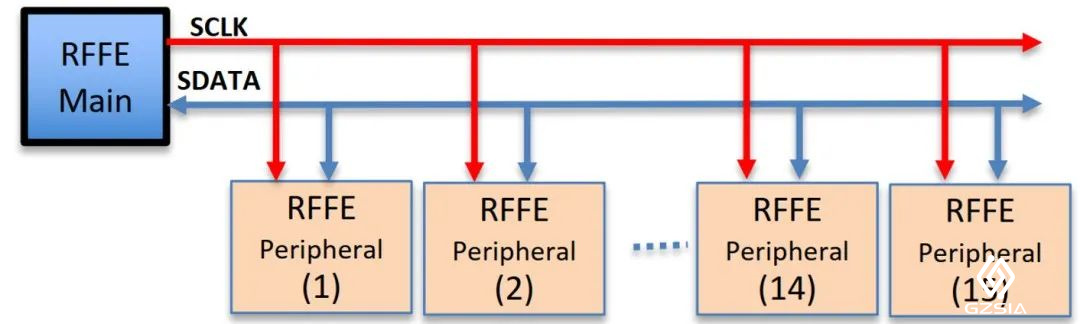

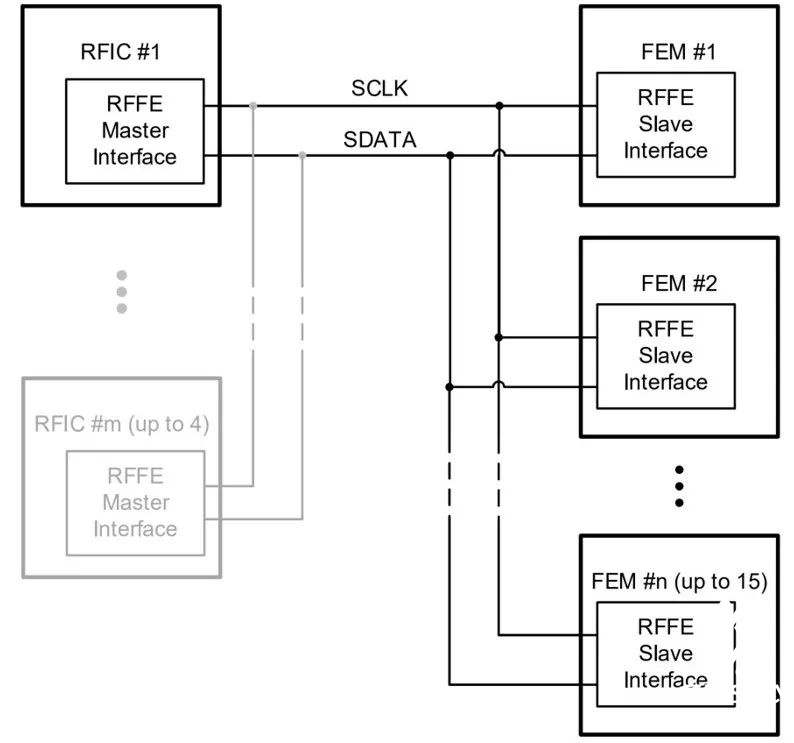

如下图是MIPI RFFE的系统架构:

图:MIPI RFFE系统架构(来自MIPI RFFE V3.0)

一个MIPI RFFE的架构通常包含:

Signal Bus:包含SCLK和SDATA两条信号线

RFFE Master Device:控制系统MIPI signal bus的器件,一般为手机系统中的RFIC(transceiver),单个MIPI系统最多可支持4个Master device

BOM:Bus Own Master,任一时刻只能有一个BOM被激活

RFFE Slave Device:MIPI受控器件,一般为射频前端模组,例如PA、LNA、Switch等,单个MIPI系统最多可支持15个device

一个Slave器件的MIPI管脚除了SCLK和SDATA还有一个VIO,这些管脚功能如下表:

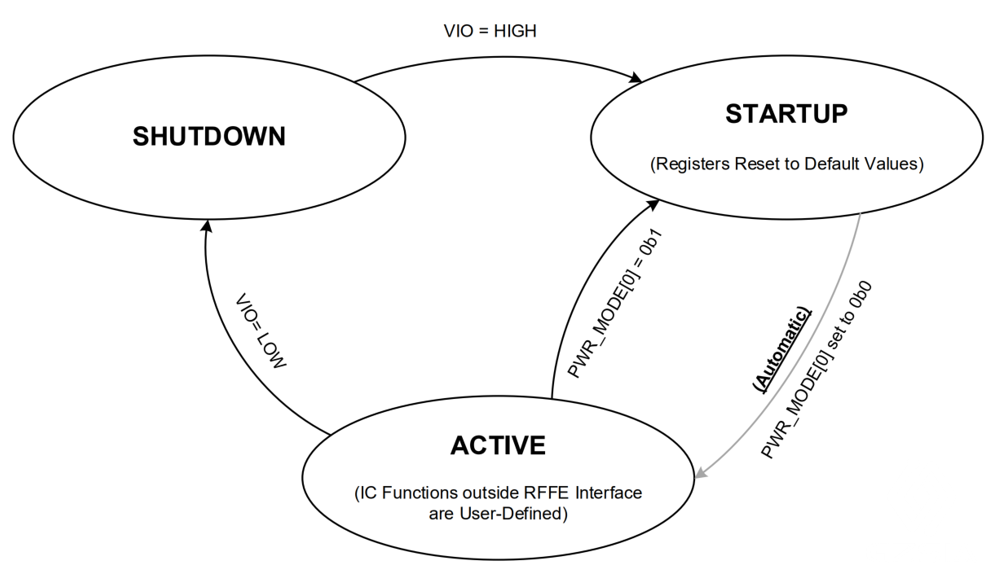

一个Slave器件会有三种状态,分别为Active、Shutdown和Startup。

图:Slave器件的三种状态:Active、Shutdown和Startup

VIO控制MIPI系统是否Shutdown

当VIO=high时,MIPI进入Startup状态,随后自动进入active状态

如需对MIPI寄存器进行重置,可发1C寄存器中PWR_MODE[0]=0b1

MIPI RFFE控制指令

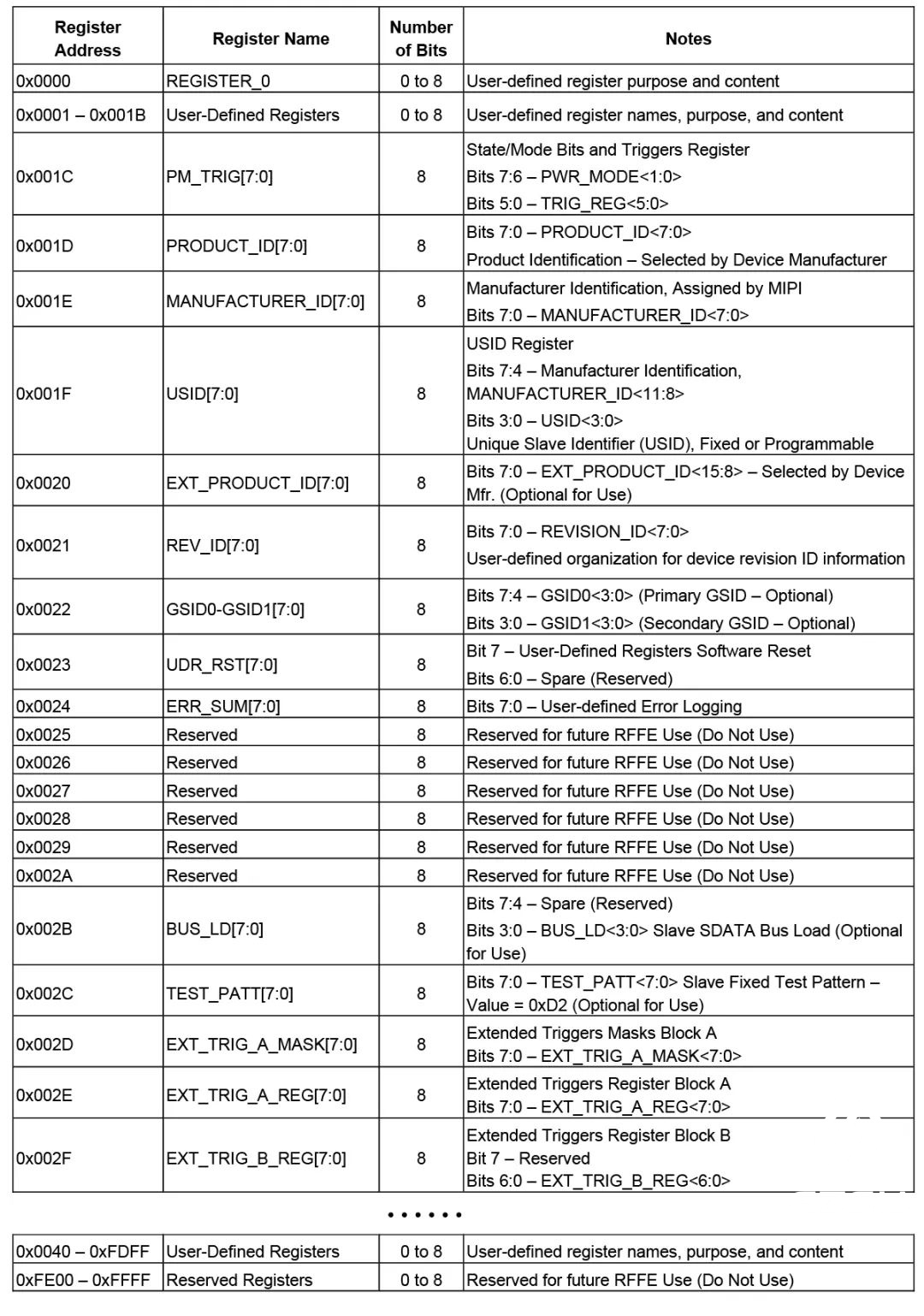

MIPI通信主要通过控制Slave器件的相关寄存器,以达到控制器件的目的。在MIPI RFFE协议中定义了多种寄存器,寄存器包含:

系统定义寄存器:系统规定有特殊应用的寄存器,如上文所提到的1C寄存器有PWR_MODE控制等

用户定义寄存器:用户可根据具体应用定义寄存器功能

图:MIPI RFFE V3.0所定义的寄存器(完整版请参与协议文档)

MIPI究竟如何使用控制指令来控制这些寄存器?

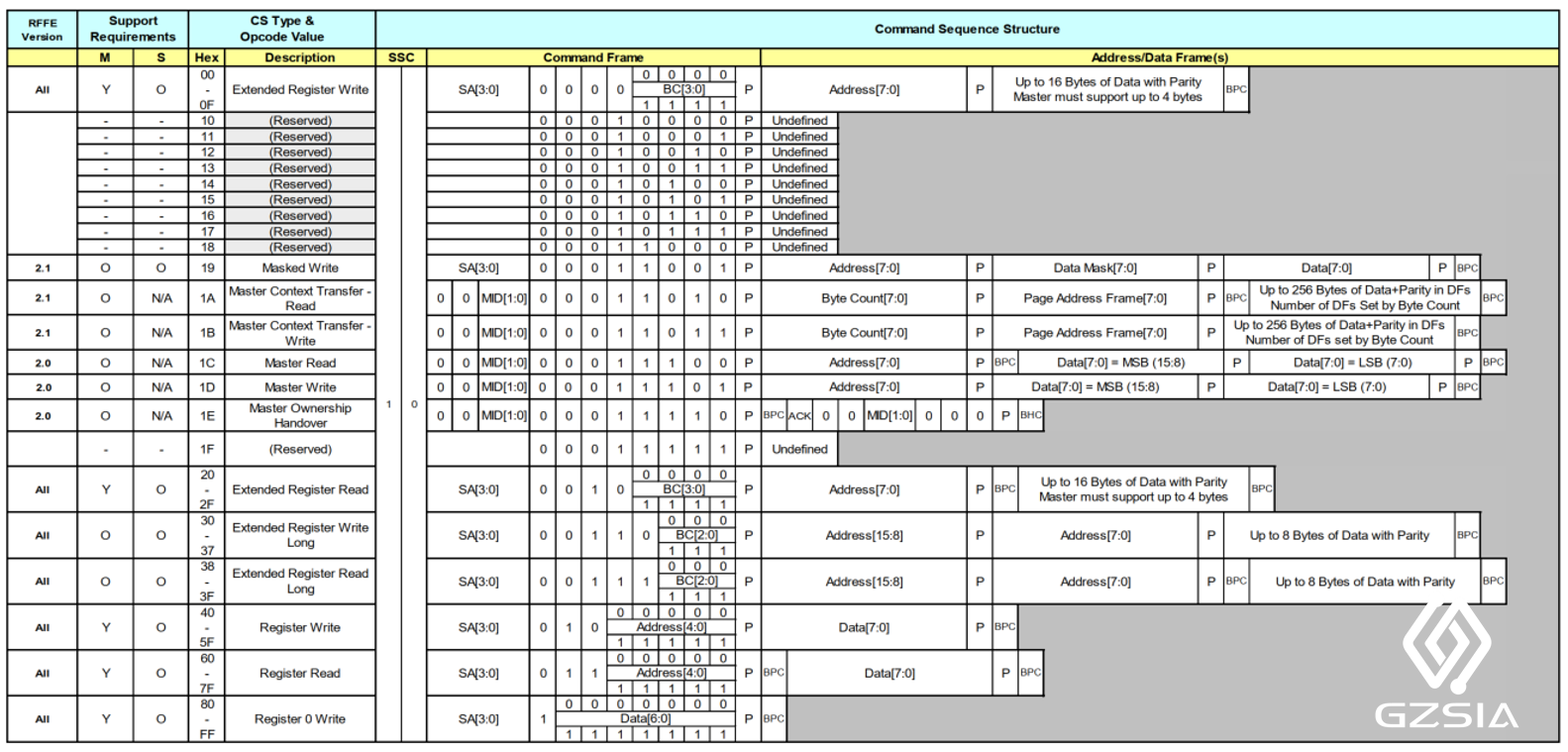

下图是MIPI RFFE各个操作的控制指令结构:

图:MIPI RFFE V3.0中所定义的控制指令结构

如上图所示,一个操作的控制指令基本会包含以下几部分:

SSC(Sequence Start Condition):指令开始标志

Command Frame:一般包含SA(Slave Address)、操作类型对应代码、以及奇偶校验码

Data Frame:不一定有,同时也包含奇偶校验码

BPC(Bus Park Cycle):指令结束标志

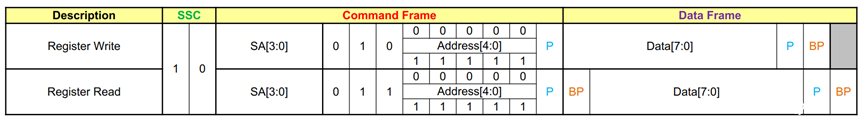

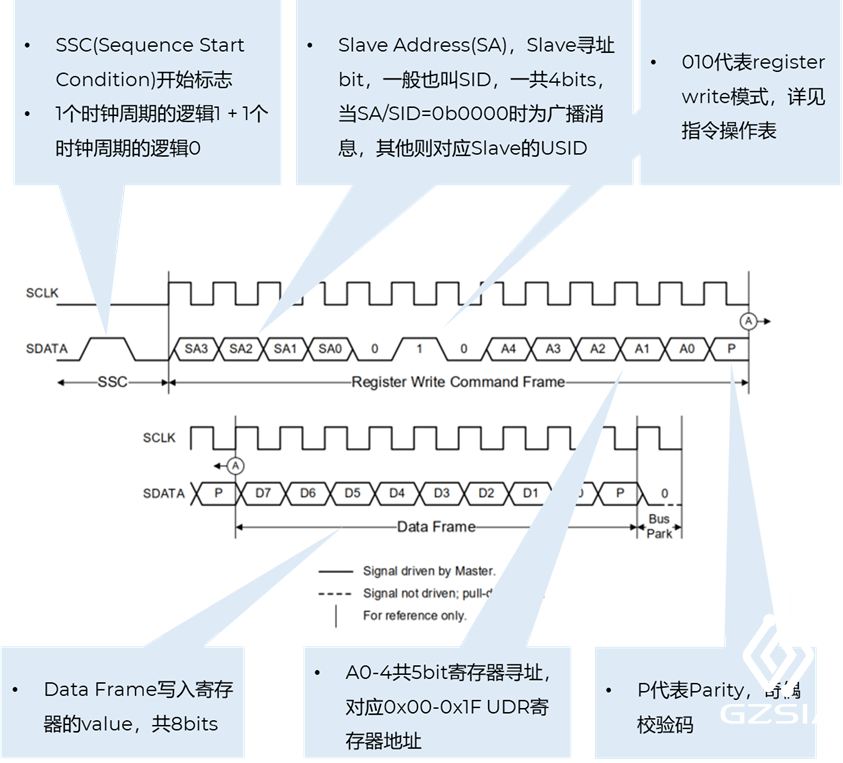

以一个最常见的控制指令寄存器写入(Register Write)为例做介绍如下:

图:MIPI RFFE中基本的写入及读取指令

图x Register Write操作指令解释

按照上图所示,如果以时钟速率52M进行计算的话,完成一次寄存器写入的指令时间大约为:1/52M*24≈0.5μs

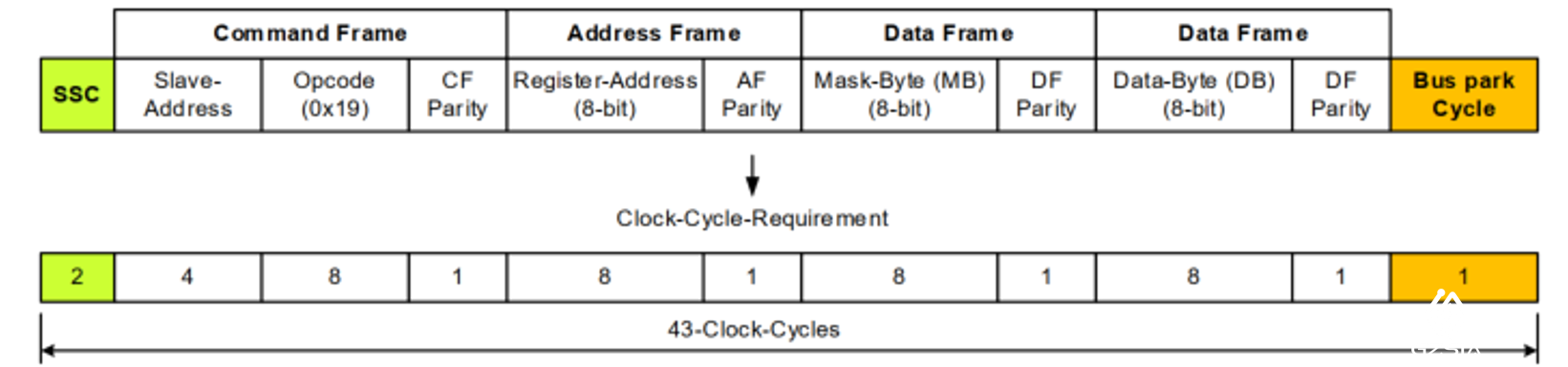

根据控制指令表,我们找到有一种更高阶的寄存器写入操作——Masked Write。Masked Write提供了一种可以可以只改寄存器部分bit位的value的方案。

例如要更新某一寄存器其中的D1/2/3/7这几个bit的值,其他bits不做更新,那么就可以采用Masked Write功能,具体指令结构和操作示意如下图:

MIPI RFFE的ID配置

MIPI RFFE中定义了多种ID,ID作为MIPI中Slave器件的识别代号有着非常重要的作用。

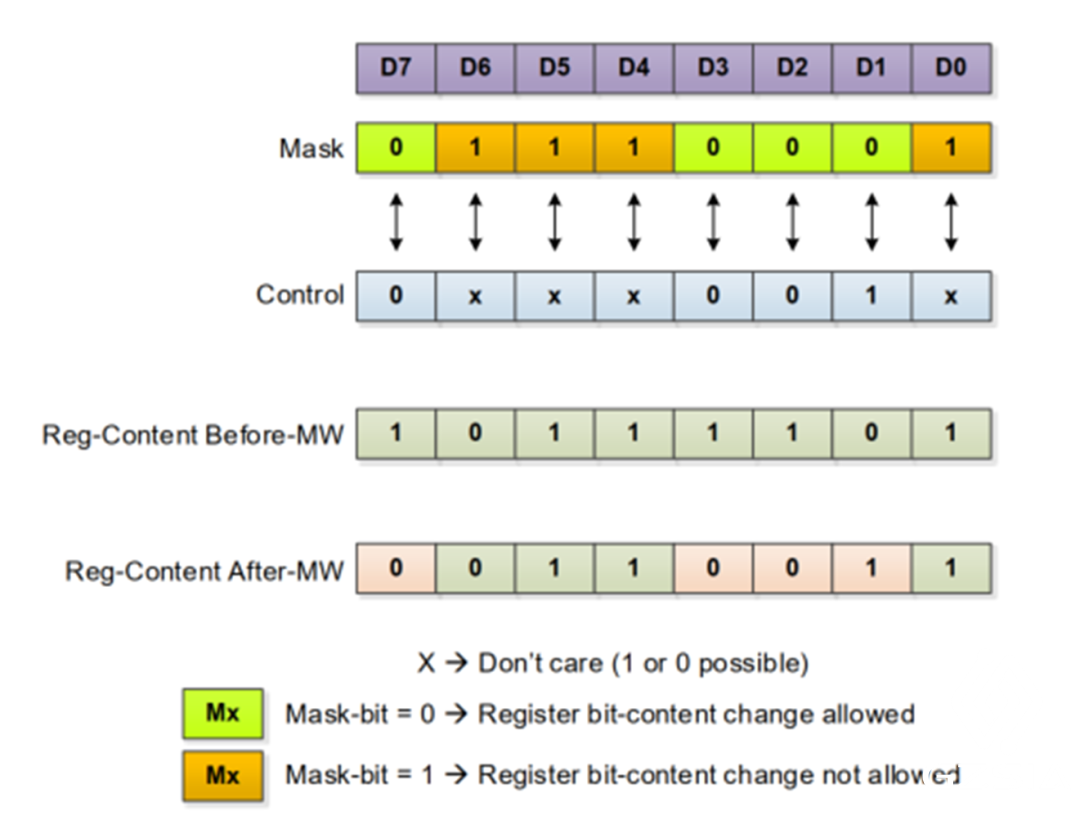

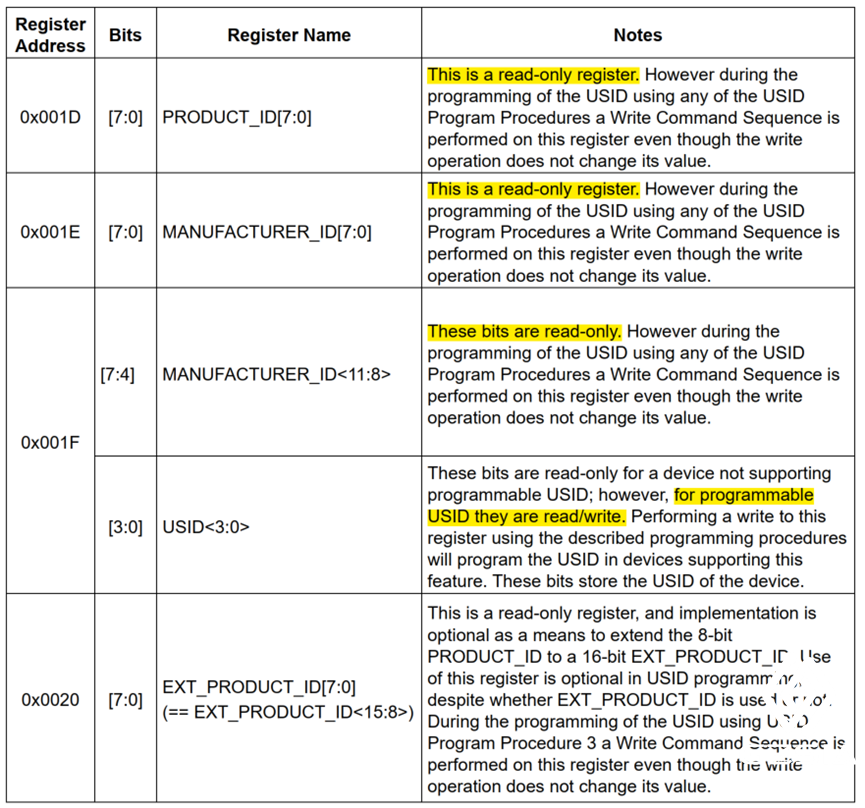

MIPI RFFE包含的相关ID以及对应寄存器地址、说明如下:

图:MIPI RFFE中所定义的多种ID说明(来自MIPI RFFE V3.0)

MID(Manufacturer ID):每个厂商在加入MIPI Alliance之后都会被分配一个专门的MID,可以从官网(https://mid.mipi.org/)查询到,例如慧智微电子分配到的MID为:2E9(hex)

PID(Product ID):由厂商自行管理给不同产品配置不同的PID,在MIPI RFFE V2.1引入了Extend-PID,这样PID就包含16bits供配置

USID(Unique Slave ID):MIPI bus主要通过USID对Slave器件进行寻址,USID共4bits 16组状态,但一个MIPI bus上最多15个Slave器件,MIPI RFFE定义SID=0b0000时为广播ID,即BSID(Broadcast Slave ID)

MID和PID所对应的寄存器都是read-only,而USID一般有一个默认的值,同时可以支持可编程。原因是MIPI指令是以USID进行寻址的,当一个MIPI bus上的所有Slave器件存在两个或以上的USID是相同的时候,会导致无法区分,因此可编程的USID至关重要。

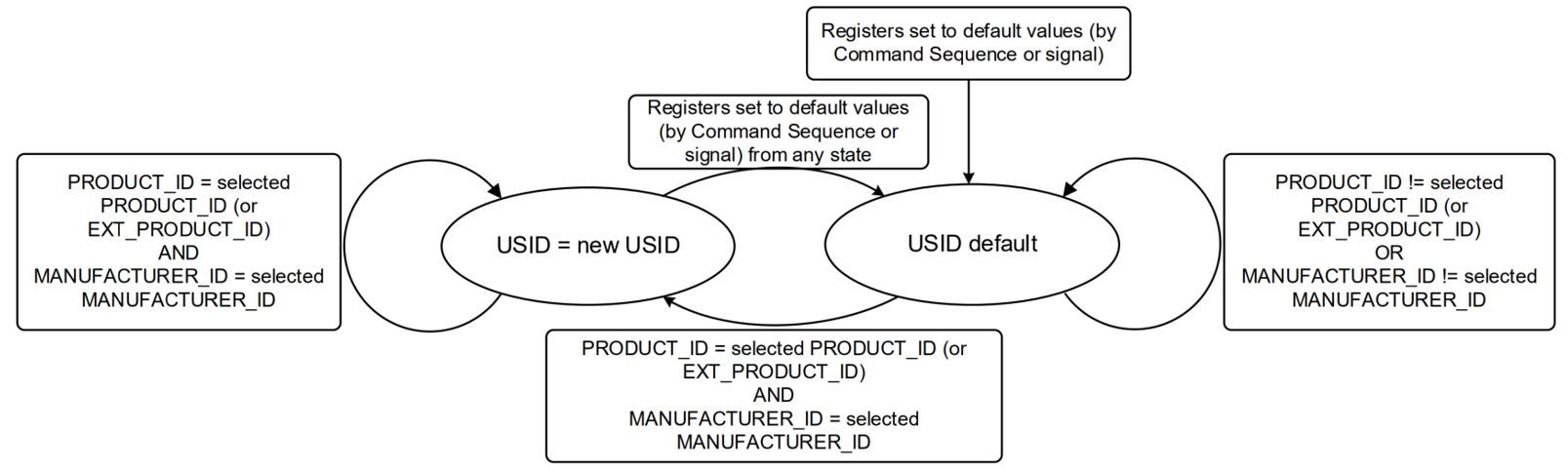

下图是可编程USID的机制图:

图:USID的编程机制(来自MIPI RFFE V3.0)

更新USID的步骤流程为:

1、通过当前USID写入PID寄存器(0x1D),写入值需要和想要更新器件的PID值相同

2、通过当前USID写入MID寄存器(0x1E), 写入值需要和想要更新器件的MID值相同

3、通过当前USID写入USID寄存器(0x1F),写入要新的USID值,当写入PID/MID与想要更新的器件PID/MID值一致时,新的USID值即生效,反之USID仍维持原来的值

简单来讲就是只有当MID/PID以及默认USID对应上之后才能够对USID进行更新,这就要求:当一个MIPI bus上挂有多个相同产品(MID/PID相同)时,为了做可编程的区分,一般会在此产品增加ID pin脚,其接高电平或GND分别对应不同的默认USID。

MIPI RFFE Trigger模式

近年来,通信协议演进至5G。5G MIMO功能需要控制射频前端多颗器件同时工作,同时5G系统用于控制的时间变短,控制接口需要以更短的时间,完成控制。

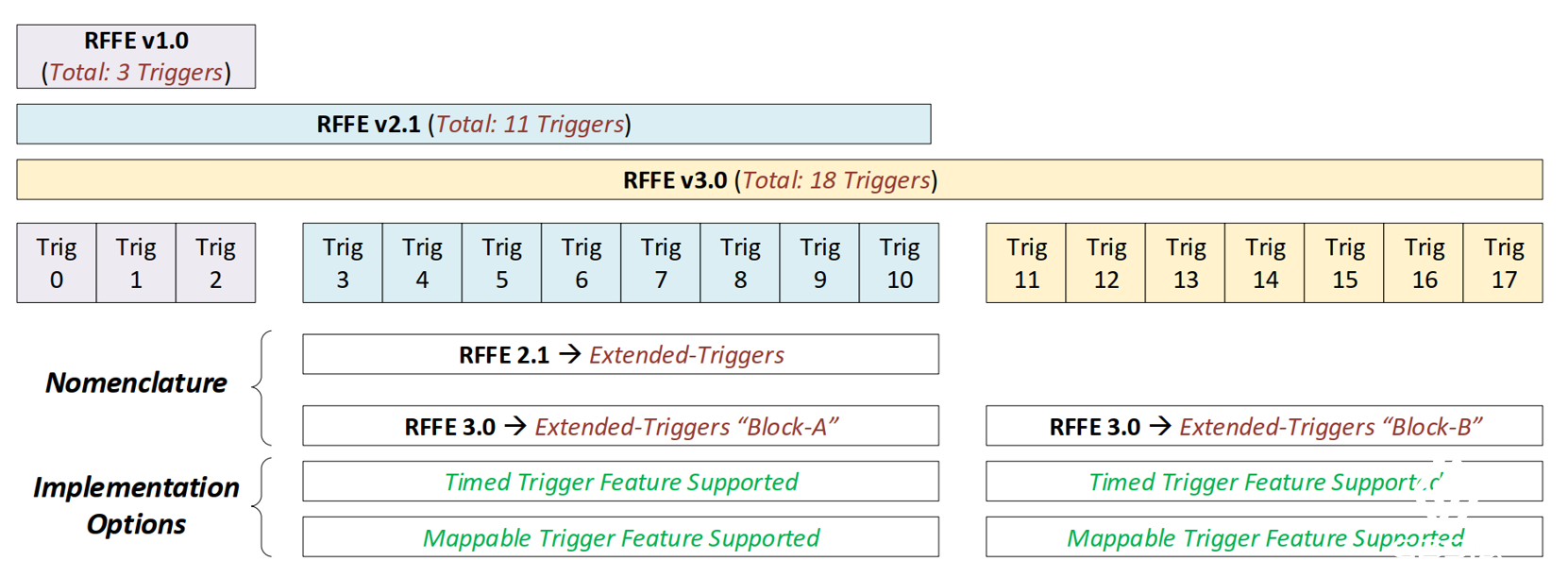

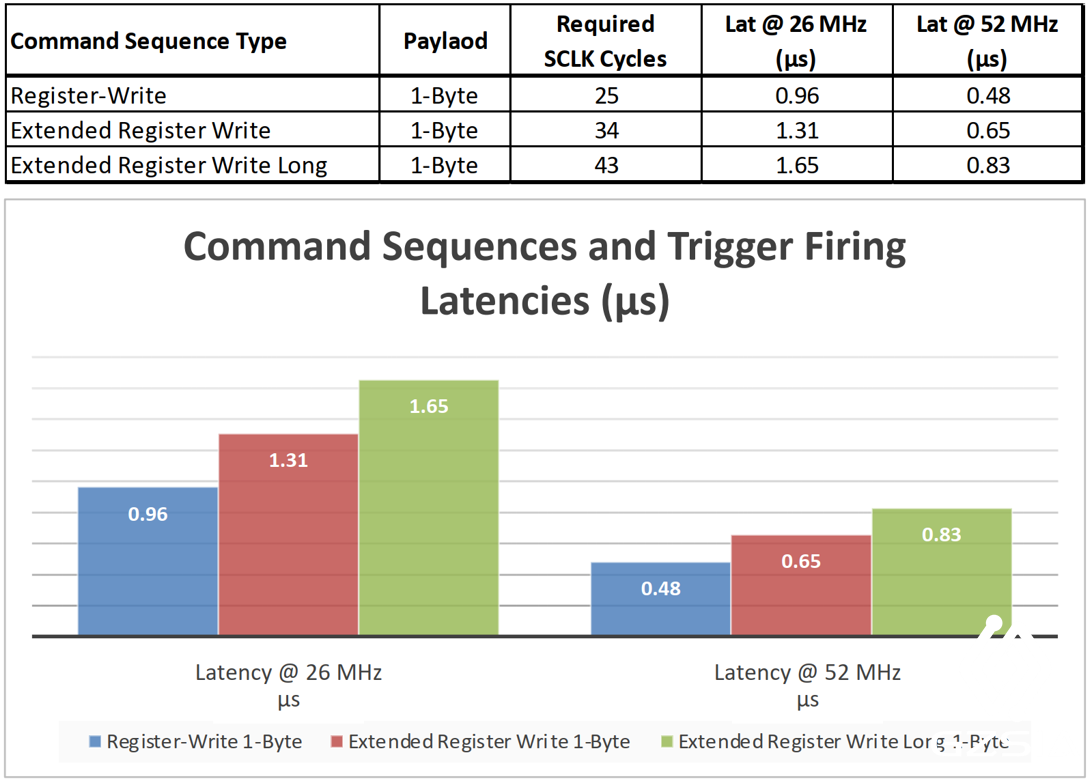

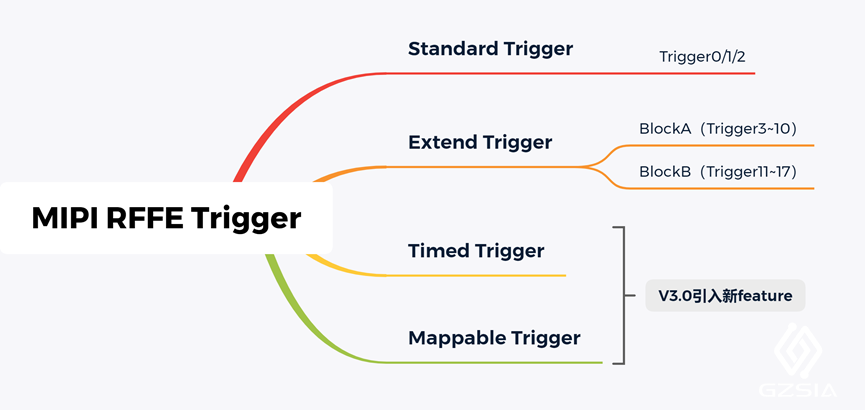

为了实现更快的控制速度,MIPI RFFE V2.0中将时钟速度由26MHz提升至52MHz,采用52MHz通信后,单个寄存器件读写的时间减少一半。但这还不足以满足5G通信系统的时序要求。为此,MIPI V3.0中着重升级了Trigger模式功能。不仅Trigger的数量由V1.0的3个、V2.1中的11个,增加至V3.0中的18个,而且还增加了Timed Trigger和Mappable Trigger功能。

图:MIPI RFFE中Trigger功能的演进

通过Trigger模式与52MHz 时钟的结合,MIPI V3.0写入指定的时间可以缩小至1μs以下。MIPI V3.0中,指令写入的时间如下图所示。

图:MIPI RFFE V3.0指令写入时间

Trigger功能的引入

当要控制一个射频芯片时,可能需要写入多个寄存器,通常可以按照串行方式每个寄存器轮流写入及生效,但由于每个寄存器生效存在时间差(以52MHz为例,每个寄存器写入时间为~0.5μs),这期间可能导致芯片工作不正常。为了解决这个问题,MIPI协议中针对UDR寄存器引入的Trigger模式,即通过Trigger功能,触发多个寄存器同时生效。

Trigger作为MIPI RFFE的重要Feature,随着5G对更多器件的控制越来越复杂,V3.0也引入了更多的Trigger功能,下图是简单的Trigger分类,本章节将一一做解释。

图:MIPI RFFE中的Trigger功能分类

Standard Trigger

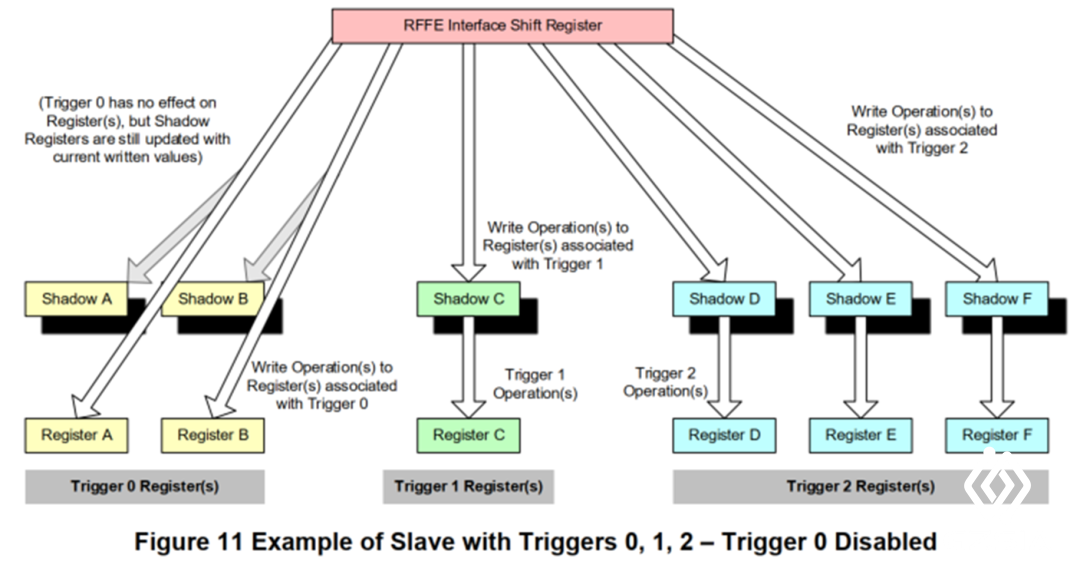

MIPI的Trigger机制如下图,为了支持Trigger模式,MIPI协议中引入了Shadow寄存器,用于存储未经触发的寄存器value:

图:MIPI RFFE中的Trigger功能

当Trigger0 disable时,此时写入寄存器A/B的值直接生效,同时A/B寄存器对应的shadow register也同时更新为写入的值;

当Trigger1/2 enable时,此时寄存器C/D/E/F的写入值首先只能更新在对应的shadow register中,只有当Trigger1执行写入操作时,寄存器C才能正式生效,同理寄存器D/E/F也需要相同Trigger2操作。

每个寄存器只能对应1个或0个Trigger。

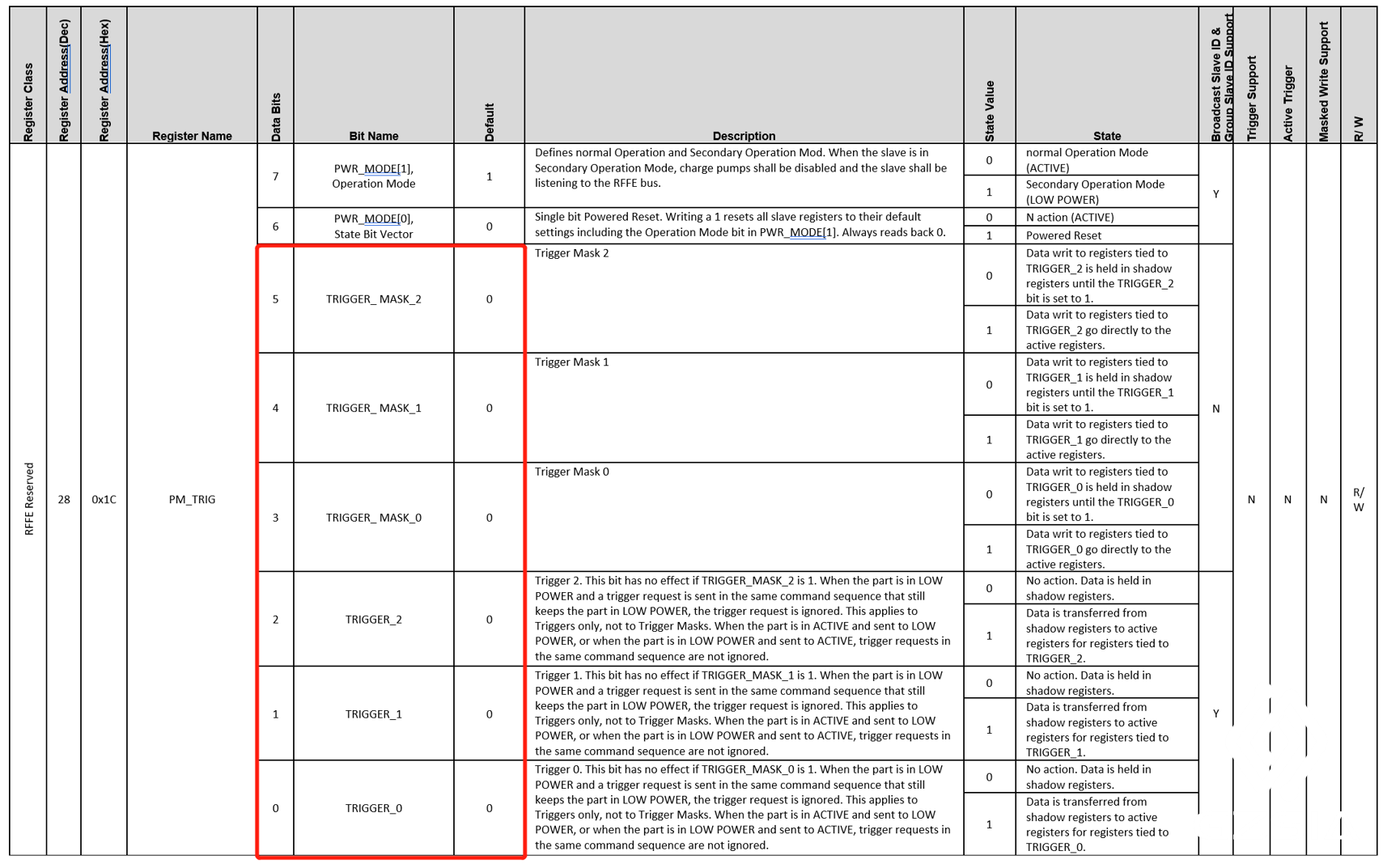

在实际操作中,MIPI RFFE中共有三个Standard Trigger,分别为Trigger0/1/2,受Reg0x1C[5:0]寄存器(见下图)控制:

0x1C[5:3]:Trigger Mask,当Trigger Mask为0时,新写入值只更新到shadow register

0x1C[2:0]:Trigger Reg,当Trigger Mask为0,且Trigger Reg=1时,shadow register的value会转移到destination register

图:MIPI table from

SmarterMicro S55255-12 L-PAMiF datasheet

举例,假设寄存器Reg01/02被设置为Trigger0控制,那么如何进行Trigger控制:

Trigger0 enable:

1. 设置Trigger0 enable,写入0x1C寄存器值为0bxxxx0xx0

2. 写入reg01/02值,值只能在Shadow寄存器中生效

3. 设置Trigger0生效,写入0x1C寄存器为0bxxxx0xx1

4. Reg01/02生效

Trigger0 disable:

1. 设置Trigger0 disable,写入0x1C寄存器值为0bxxxx1xx0

2. 写入reg01/02值,直接生效

Extend Trigger

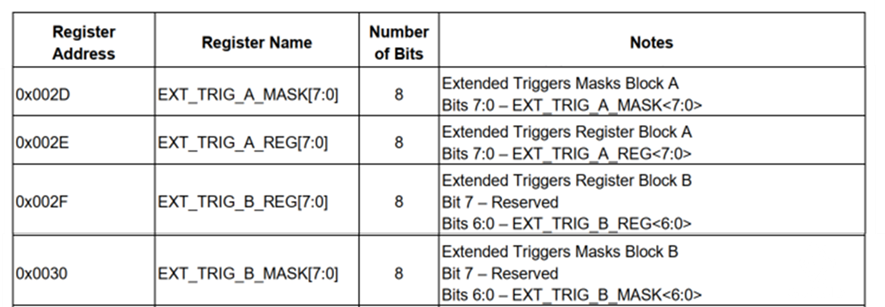

为了支持更多的寄存器Trigger数量,MIPI RFFE V2.1/3.0分别各引入了8个Trigger,工两组Block A和BlockB,统称为Extend Trigger。

Extend Trigger的控制和Standard Trigger一样,对应的寄存器为0x2D~30,如下表:

需要注意的是,下文要讲的Timed Trigger和Mappable Trigger只能应用于Extend Trigger,不能用于Standard Trigger。

Timed Trigger

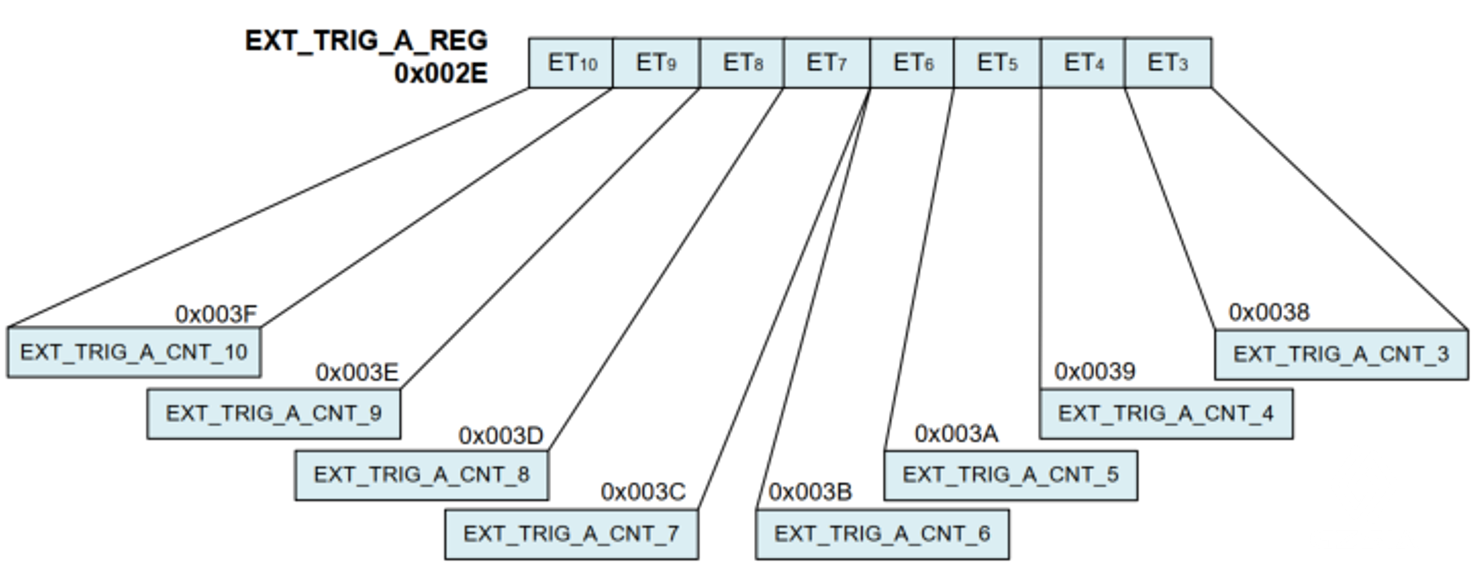

Timed Trigger顾名思义是在时间上对Trigger进行操作,具体就是提供寄存器在延时一定时间后生效,主要机制是对Trigger设置延时计数器生效。

对应的延时计数器其实是由一个延时的计数寄存器进行控制,如下图是BlockA Extend Trigger对应的Counter register:

Timed Trigger的工作机制如下:

当counter register的值=0,则此Extend Trigger属于正常Trigger

当counter register的值为非零时,寄存器的数则跟随时钟开始倒计时,直到值=0,Trigger生效

Mappable Trigger

如上介绍,我们了解到每个寄存器有且最多只能配置对应一个固定的Trigger,但随着5G的加入,射频前端越来越复杂,例如以下场景:

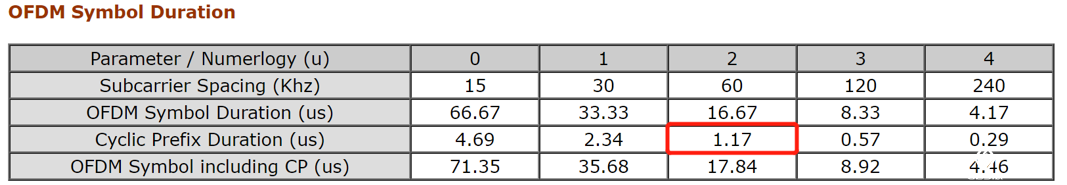

在5G手机中,可能有超过8路接收通路同时工作(CA场景),此时就需要同时控制8路LNA进行快速的AGC,每路LNA至少需要发送一个寄存器(~0.5us),然而5G的AGC切换是在symbol之间进行,而symbol与symbol之间只有一个CP的时间长度(当SCS=60kHz,时间为1.17us,如下图)来完成写入寄存器+LNA gain settle时间。因此要同时串行发送以上多路LNA是无法完成的。

Mappable Trigger提供这样一个可能,对寄存器不配置固定的Trigger,而是可编辑的Trigger,这样通过把所要控制的所有寄存器都配置到相同的Trigger,那么就可以在正式生效前坐pre-setting,然后再同时Trigger。

Mappable Trigger具体操作如下:

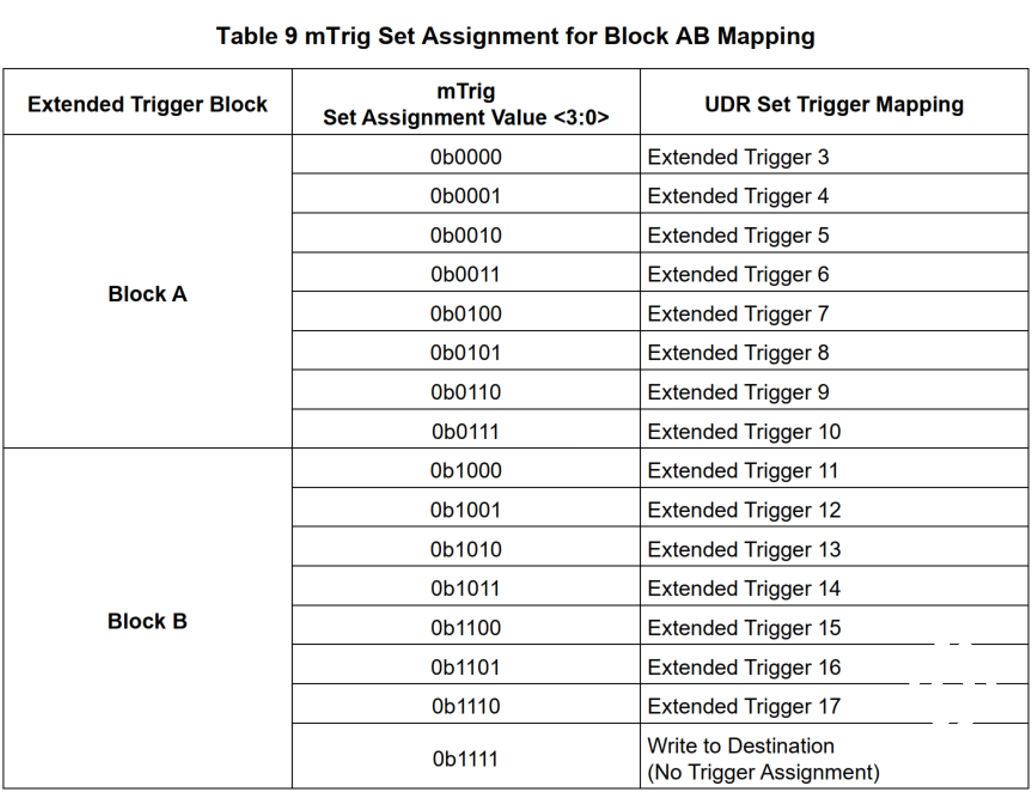

1. 定义一个寄存器叫mTrig set,4个bits对应一个BlockA/B Extend Trigger,如下图;

2. 一个UDR寄存器最多只能配置一个mTrig set,或一个Fixed Trigger,不同同时配置两种Trigger;

3. 当某个寄存器被配置为mTrig setA,且此时mTrig setA被写入成0b0010时,查表对应的Extend Trigger是ET05,则Extend Trigger05为当前寄存器及所有配置为mTrig setA的寄存器对应的Trigger;

4. 当mTrig setA的值更新后,对应的Trigger也会同时更新;

5. mTrig不会影响Timed Trigger,二者相互独立。

02 MIPI RFFE协议的未来发展

随着协议演进,射频前端功能越来越复杂;同时射频前端器件与基带控制间的关系越来越紧密,高通公司表示未来通信系统中Modem将越来越多的与射频前端进行联合设计。以上两点都对RFFE与Modem之间的接口:MIPI RFFE接口提出更高的要求。

图:高通公司将Modem与RFFE进行联合设计

在MIPI RFFE V3.0发布之后,目前MIPI联盟RFFE工作组在讨论之中的更新有:

加入5G通信中的新特性,甚至6G演进中的新需求。

考虑5G NR FR2(毫米波)频段的需求和挑战。

会员单位提出的其他新需求。

可以预计,MIPI RFFE的未来将更加强大。预计未来在应用中使用到的MIPI RFFE功能有:

MIPI RFFE继续成为移动终端的标准通信接口,并且应用领域不断扩大。

Trigger模式的灵活运用,以满足协议苛刻的时序要求。

更多寄存器控制支持,以满足日益复杂的器件接口控制功能。

以上为慧智微在与MIPI联盟RFFE工作组工作,以及公司5G器件开发过程中对MIPI RFFE技术的了解,您在使用过程中对MIPI RFFE协议技术有什么理解或者问题,欢迎留言讨论。

参考文献:

1 MIPI RFFE V3.0协议:mipi_RFFE_specification_v3-0.pdf

2 MIPI RFFE V2.1协议:mipi_RFFE_specification_v2-1.pdf

3 MIPI Alliance website: https://www.mipi.org/

4 慧智微产品规格书:SmarterMicro S55255-12 UHB_L-PAMiF Datasheet v1.74.pdf

5 http://www.sharetechnote.com/

注:本文转载自慧智微电子